Keysight Chiplet PHY Designer: Giải pháp mô phỏng kết nối IP D2D sang D2D PHY theo chuẩn UCIe™

Giải pháp Chiplet PHY Designer, thành viên mới nhất trong dòng công cụ mô phỏng và thiết kế số tốc độ cao của doanh nghiệp Keysight, với chức năng mô phỏng kết nối đế-đế (D2D), một bước đi quan trọng trong việc xác minh hiệu năng cho các thiết kế 3D mạch tích hợp (IC) không đồng nhất thường được gọi là chiplets.

- Keysight xác nhận hợp chuẩn trường hợp kiểm thử đầu tiên theo tiêu chuẩn 3GPP Release 17 cho mạng vệ tinh

- Keysight cung cấp phần mềm giúp tối ưu thời lượng pin

- Keysight Technologies ra mắt giải pháp đo kiểm hiệu năng sóng milimet cải tiến trong mạng 5G

- Keysight được lựa chọn để hợp quy các thiết bị 5G, Wi-Fi và Bluetooth

- Keysight được phê duyệt cung cấp hệ thống đo kiểm OTA 5G mmWave

- Keysight giới thiệu công nghệ kiểm thử tự động tiên tiến cho ứng dụng di động

- Bước tiến quan trọng của Keysight và Ettifos trong bài đo sidelink theo tiêu chuẩn 3GPP Release 16

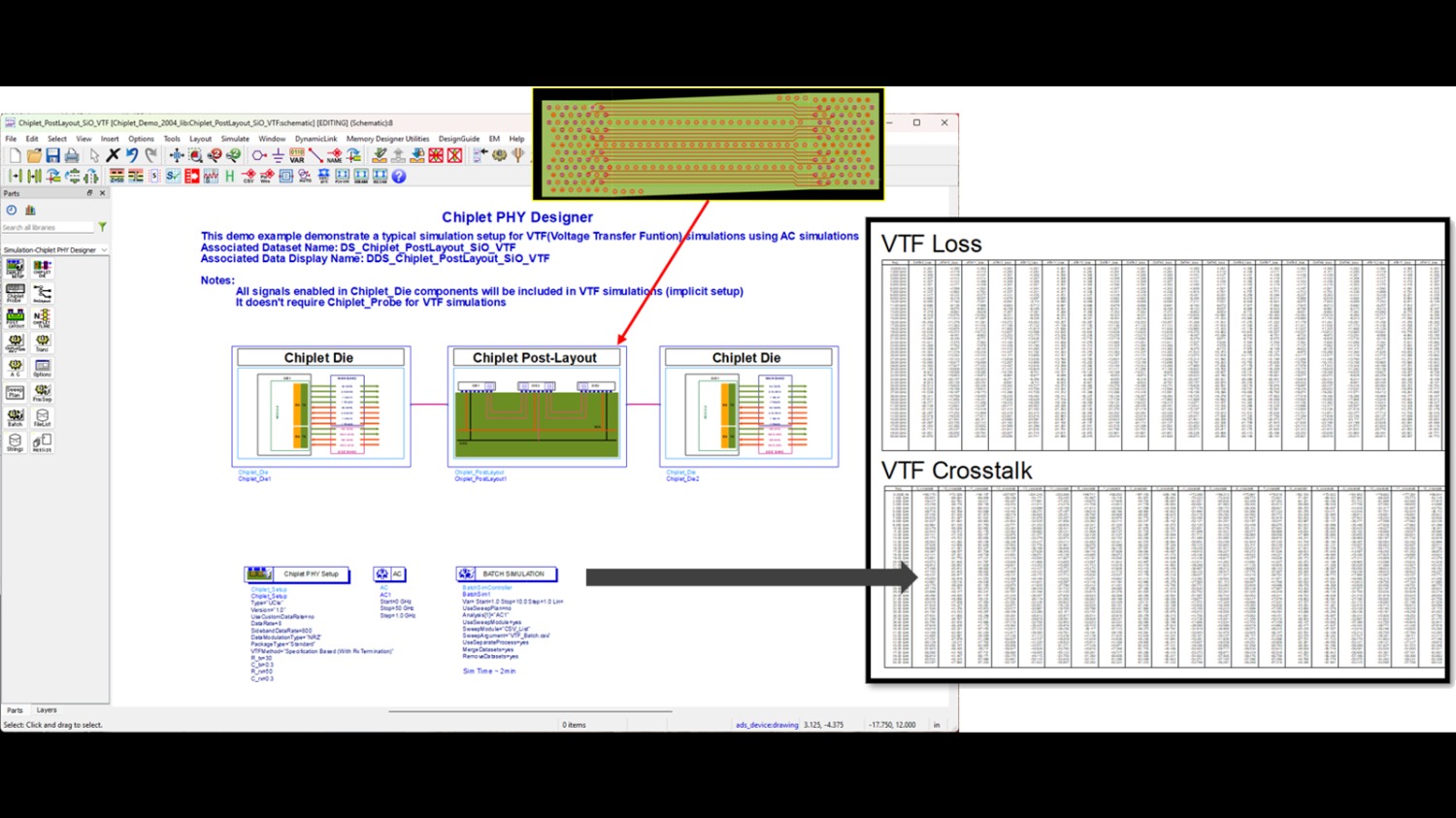

Cụ thể, công cụ tự động hóa thiết kế điện tử (EDA) mới này là công cụ đầu tiên trên thị trường có khả năng mô hình hóa và mô phỏng chuyên sâu, cho phép các nhà thiết kế chiplet nhanh chóng xác minh chính xác rằng thiết kế của họ đáp ứng các thông số kỹ thuật của tiêu chuẩn Universal Chiplet Interconnect Express™ (UCIe™).

UCIe đang được xem là bộ thông số kỹ thuật kết nối chiplet hàng đầu trong ngành bán dẫn. Tiêu chuẩn mở này xác định kết nối giữa các chiplets được đóng gói 2.5D nâng cao hoặc 3D. UCIe đang được nhiều nhà cung cấp thiết bị bán dẫn và công cụ EDA hàng đầu cũng như các xưởng đúc và nhà thiết kế chiplet từng bước hỗ trợ và ứng dụng.

Khi sử dụng tiêu chuẩn kết nối này và đảm bảo các chiplets của họ đáp ứng các thông số kỹ thuật của nó, các nhà thiết kế đang giúp thiết lập một hệ sinh thái rộng lớn đáp ứng khả năng tương tác và thương mại hóa các chiplet.

Đội ngũ nghiên cứu phát triển của Keysight EDA đã có lịch sử nhiều thập kỷ nghiên cứu phát triển khả năng mô hình hóa và mô phỏng các giao diện số tốc độ cao phù hợp với các thông số kỹ thuật trên thị trường. Chẳng hạn: công cụ ADS Memory Designer mô phỏng giao diện bộ nhớ toàn diện như GDDR7, DDR5, LPDDR5 và HBM3 với bộ lập mô hình IBIS-AMI. Giải pháp đo kiểm tuân thủ JEDEC nghiêm ngặt và độc đáo của Keysight xử lý hơn 100 ID đo bằng cùng thuật toán đo kiểm trong dòng máy hiện sóng Keysight Infinium.

Các tính năng chính của bộ mô phỏng lớp vật lý Chiplet PHY Designer bao gồm:

-

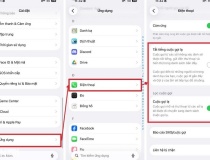

Hỗ trợ tiêu chuẩn lớp vật lý UCIe - tự động phân tích tín hiệu theo các quy ước đặt tên tiêu chuẩn, kết nối tự động giữa nhiều đế qua liên kết gói, thiết lập mô phỏng theo tiêu chuẩn như loại tốc độ và thiết lập đo lường trực quan thông qua các đầu dò chuyên biệt.

-

Đo chức năng truyền điện áp (VTF) - tính toán chính xác VTF để đảm bảo tuân thủ thông số kỹ thuật của UCIe và phân tích tỷ lệ lỗi bit của hệ thống (BER) tới mức 1e-27 hoặc 1e-32. Đo chiều cao sơ đồ mắt, chiều rộng mắt, độ lệch, lề mặt nạ và đường viền BER.

-

Phân tích định thời từ nguồn ngoài để đo chính xác chức năng định thời dị bộ.

Adrien Auge, Kỹ sư ứng dụng cao cấp, Alphawave Semi, cho biết: "Alpha Wave Semi cần có khả năng xác nhận các giải pháp chiplets để tạo ra thiết kế chip không đồng nhất, vì chức năng này đảm bảo hoạt động liền mạch và khả năng tương tác cho các giải pháp 2.5D/3D cho khách hàng của chúng tôi. Công cụ Chiplet PHY Designer đơn giản hóa quy trình mô phỏng điện cho kết nối đế-đế lớn, chẳng hạn như UCIe.

Công cụ này cho phép các kỹ sư và nhà thiết kế nhanh chóng và dễ dàng xác định tính tuân thủ điện của các giải pháp của họ theo các thông số kỹ thuật mới nhất. Hơn nữa, nhờ tuân thủ các chỉ tiêu kỹ thuật lập mô hình IBIS mới nhất cho I/O điện, các nhà tích hợp vật lý có thể tập trung hơn vào quá trình xác nhận tuân thủ tiêu chuẩn điện của chiplet, phát huy các mô hình chi tiết của chúng tôi để có được dự đoán hiệu năng trước khi sản xuất silicon.”

"Đội ngũ mô phỏng số tốc độ cao của chúng tôi đã vận dụng những hiểu biết của họ về những khó khăn của việc đo kiểm sớm hơn các thiết kế SerDes PHYS. Họ đã áp dụng những kiến thức này vào lĩnh vực chiplet áp dụng thành công chiến lược mô phỏng theo tiêu chuẩn của chúng tôi sang chuẩn UCIe. Mô hình hóa kết nối là yếu tố thiết yếu đối với thiết kế và hiệu năng hệ thống. Công cụ Chiplet PHY Designer rút ngắn thời gian xác nhận các tiểu hệ chiplet, từ một D2D PHY qua các kênh kết nối với một D2D PHY khác, và bắt đầu xác nhận sớm hơn nhiều trong chu kỳ thiết kế. Công cụ này cho phép các nhà thiết kế vi mạch 3D giải quyết các vấn đề quan trọng về hiệu năng kết nối, cải thiện khả năng tạo mô hình nguyên mẫu với khả năng dự đoán để tăng tốc độ đưa sản phẩm ra thị trường." Niels Faché, Phó Chủ tịch kiêm Tổng Giám đốc, Keysight EDA, cho biết.

Theo tạp chí Điện tử & Ứng dụng